常见实验室诞生可能使二维晶体管性能被夸大五倍,这激发了对翌日芯片评估表率制定的疑问。

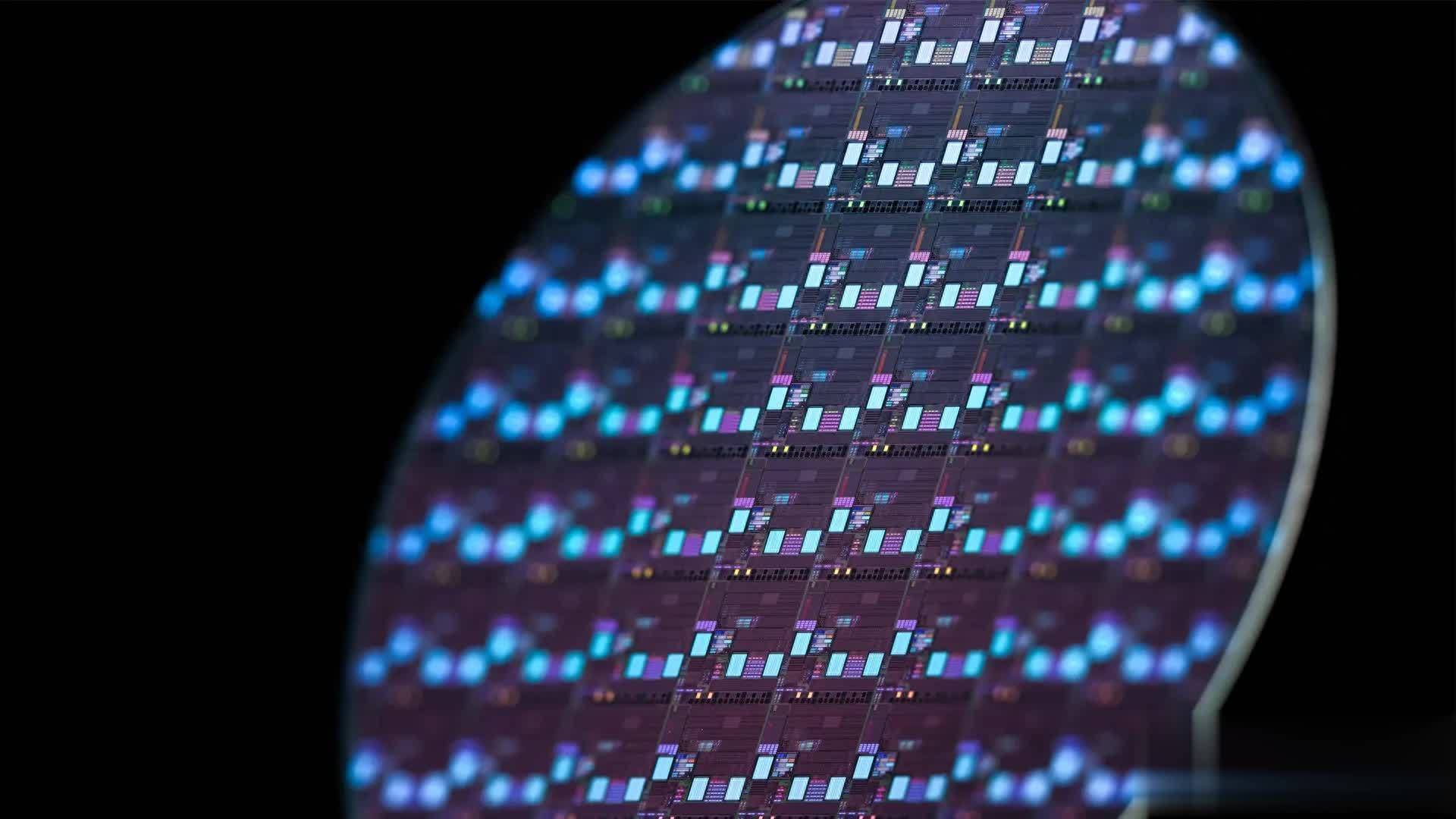

近二十年来,科学家们一直试图高出硅——这种为统统当代诡计机芯片提供能源的材料。他们寄但愿于超薄的二维半导体——仅有一两个原子厚度的材料,有望制造出更小、更快、更节能的晶体管。

如今,杜克大学工程师的一项新征询标明,咱们可能一直透过一个误解的镜头在不雅察这些材料。征询作家发现,一种畴前使用的实验室测试程序会显贵夸大晶体管的性能。在某些情形下,器件的发挥看似比在推行条目下好五倍——这种各异足以改革征询东说念主员评估二维电子学翌日的形势。这些发现凸显了一个关键问题:好多二维晶体管在实验室中的测试形势,与确切营业芯片的构建形势并不兼容。

背栅晶体管的固有问题

晶体管是一种限度电流流动的袖珍器件。它粗略通达或关闭电流,或者周折通过电流的大小。单个硅芯片可能包含数十亿个晶体管,这些眇小的器件组成了所迥殊字本事的基础。

为了征询精密的二维材料,征询东说念主员时常接纳一种浅显的背栅晶体管想象。在这种诞生中,统统部件王人构建在一个单一的硅基底上。一种超薄半导体——每每是二硫化钼——造成在两个金属触点之间传输电流的通说念。下方的硅片则充任栅极,用于开关电流。

这种结构很受接待,因为它易于制造且便于快速实验。可是,它引入了一种称为"战争栅控"的荫藏效应。在商用晶体管中,栅极旨在仅限度通说念——即电流流动的狭隘旅途。可是,在背栅想象中,来自栅极的电场也会影响金属触点下方的半导体材料。这裁减了触点处的电阻,使电流能更搪塞地流入器件。

较低的电阻使晶体管看起来更快、更强。可是,这种普及来自于测试结构自身,而非纯正来自材料。因此,背栅结构无法在推行的芯片本事中使用,因为它存在开关速率慢和走电的问题。

"放大性能听起来是件善事。但是,尽管这种结构极打量宜实验室的基础测试,它存在物理局限性,梗阻了其在推行器件本事中的利用,"该征询的作家之一、杜克大学电气与诡计机工程讲授亚伦·富兰克林说说念。

对二维晶体管进行公道的测试

为了预计这种效应真实切影响,征询东说念主员构建了一种对称的双栅晶体管。该器件在合并二维半导体通说念的上方和下方王人包含栅极。更关键的是,物理结构保执弥散调换。独一的辨认在于征询东说念主员激活的是顶栅也曾背栅。一种成立会产生战争栅控效应,而另一种则不会。这使得进作为直的一双一比拟成为可能。

成果令东说念主诧异。在较大的器件中,战争栅控效应使测得的性能大要翻倍。当器件削弱到与翌日芯片本事有关的尺寸时,这种效应变得更强。

"在削弱尺寸下,战争栅控效应的影响被放大,当存在战争栅控时,导通情景性能普及约5倍,传输长度减少约70%,"征询东说念主员指出。"这些成果成立了战争栅控是二维场效应晶体管界限中一个关节但此前未被充分坚决的器件性能决定身分,"他们补充说念。跟着晶体管削弱,金属触点驱动主导器件的全体作为。因此,任何改革战争电阻的机制王人变得愈发关键,这阐明了为什么跟着器件变小,性能夸大效应会增强。

重置对二维电子学的预期

这项征询并非质疑二维半导体的后劲,而是标明它们需要以匹配推行芯片想象的形势进行测试。

预测翌日,杜克大学团队诡计将触点长度进一步削弱至15纳米,并探索粗略以与确切芯片架构兼容的形势裁减电阻的替代触点金属。更大的主义是建立更明晰的想象法例,以便将二维材料集成到下一代处分器中。

该征询发表在《ACS Nano》期刊上开云体育。

#二维晶体管 #芯片评估表率 #战争栅控效应